2.5D / 3D 패키징 기술 진화

TSMC의 CoWoS-S 에서 CoWoS-L/CoWoS-R 로 진화.

> Hybrid bonding / CMP / 화학 및 기계적 연마 같은 기술들 필요로 할 것<CMP-케이씨텍, 하이브리드본딩-BESI, 한미반도체, 한화인더스트리얼솔루션즈, 미코(부품, 펄스히터)>

> 검사 / 계측 정밀 기술 요구

> 실리콘 포토닉스<브로드컴, 코히런트> (SoIC라는 3D 패키징 기술에다가 COUPE라는 실리콘 포트닉스 기술을 하기로 하면서 2027년 예정이던 게 앞당겨지는 그림) ~> CPO라는 새로운 콘셉트의 패키징 기술의 고도화 이끌어 냄.

> 글래스 코어 기판<삼성전기, SKC(앱솔릭스), 필옵틱스(SKC향), HB테크놀로지(삼성전기향)>

>2nm GAA<솔브레인(초산계 에천트), 파크시스템스(원자 현미경)>

이는 AI 가속기, AI 데이터센터 등의 수요 늘어남. 생성형 AI의 수익화가 가능해지며 비싼 기술들을 더 활용할 수 있게 됨.

TSMC 패키징기술 InFO(2D) vs CoWoS(2.5D) vs SoIC(3D)

InFO(2D)

InFO(Integrated Fan-Out)는 Substrate를 사용하지 않고 웨이퍼 위에 RDL(Re Distribution Layer)을 형성해 패키징 하는 기술로 Advanced packaging 중 가장 먼저 도입

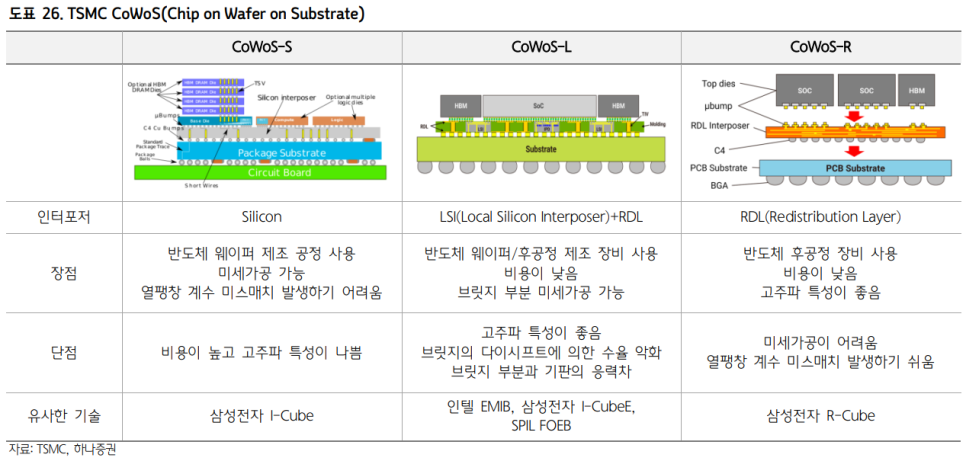

CoWoS-S & CoWoS-L & CoWoS-R

CoWoS(Chip on Wafer on Substrate)는 말 그대로 실리콘 인터포저 위에 칩을 연결한 후 Substrate에 연결하는 방식으로 현재 AI 반도체 생산에 가장 보편적으로 이용되는 패키징 기술. Nvidia의 H100, H200, AMD의 MI300은 모두 CoWoS-S를 채택했으며 Nvidia는 Blackwell 플랫폼부터는 CoWoS-L을 채택할 전망.

SoIC

SoIC(System on Integrated Chips)는 마이크로 범프 없이 칩을 3D 구조로 적층하는 패키징 기술이다. 하이브리드 본딩 방식으로 마이크로 범프 없이 구리패드를 접촉시켜 연결하기 때 문에 고밀도로 패키징 할 수 있고 신호 전달 경로가 짧아져 기존 패키징 방식 대비 속도와 전력 효율이 우수하다는 특징. AI 확산으로 데이터 처리량이 증가하며 칩 성능을 향 상시키기 위해 다수의 팹리스 기업들이 AI 칩 내 SoIC 기술 적용을 검토중.

'용어정리' 카테고리의 다른 글

| HBM 벨류체인 (0) | 2025.01.09 |

|---|---|

| 훅업(Hook-up) 공사와 1차배관 2차배관(feat. 산업 현장에서의 유틸리티 뜻) (1) | 2024.12.04 |

| 해상풍력발전 개요 및 산업동향과 전망 (1) | 2024.11.30 |

| 반도체 광학검사장비의 종류: Bright field(브라이트필드) vs Dark field(다크필드) vs macro(매크로) (0) | 2024.11.26 |

| PECVD ( Plasma Enhanced Chemical Vapor Deposition)란? (feat. ACL, ARC) (0) | 2024.11.24 |